## Real-Time Self Repairable Multiplexer for Fault Tolerant Systems

G. Divya<sup>1</sup>, Addanki Dharani<sup>2</sup>, N. Gayathri<sup>3</sup>, .K. Ashok Reddy<sup>4</sup>

<sup>1,2,3</sup>Research Scholar, Vignan Institute of Management and Technology for Women, Kondapur, Ghatkesar, Medchal -50130.

<sup>4</sup>Assistant Professor, Vignan Institute of Management and Technology for Women, Kondapur,

Ghatkesar, Medchal -50130.

### Abstract

More transistors may be put on a single chip when using VLSI. The system or chip is increasingly prone to errors when the distance between transistors or circuits decreases. Inaccurate outcomes must be prevented via fault tolerant systems. A device called a multiplexer chooses input signals depending on a choose signal. The sole self-checking multiplexer is the subject of the current works.

A self-repairing 2:1 multiplexer that can fix both permanent and temporary errors is suggested in this research. The self-repairing multiplexer is offered with two distinct designs. The first design includes extra circuitry to fix the multiplexer problem. The OR and AND gates that make up a multiplexer are selfrepairable in the second design. The single and multiple defects may be detected and fixed by these self-repairing multiplexer suggested architectural designs. The designs provide 100% error recovery. With the help of the Cadence tool, the functioning of the circuits is checked.

**Index Terms**— VLSI, Fault, Error, Self-checking, Self-repairing.

## **I. INTRODUCTION**

A circuit's answer might be invalid due to the existence of faults. This yields

unreliable outcomes. To endure errors, systems that are fault-secure are very

necessary. Therefore, self-checking and self-repairing are essential for the circuit to operate properly. In self-checking, the circuit itself finds the issue, and in selfrepairing, the circuit may fix itself and provide the desired output. Individual circuit gates affect how well a circuit performs overall. Designing with fewer gates may improve performance in terms of delay, area, and power.

The critical route should be as short as feasible to achieve high speed. Similar to this, fewer gates are employed at the circuit level to achieve low power without sacrificing the circuit's precision. A broad range of applications, including adders, multipliers, communication, digital signal processing, etc., employ multiplexers.

The input data will be chosen by the multiplexer and sent to the output based on the selection signal. Incorrect data is produced when a multiplexer is malfunctioning. In order for the multiplexer to produce accurate data even with faults, it must be fault secure.

### **II. EXISTING SYSTEM**

In existing model the full adder which consists of AND, OR gates and 2X1 MUX are designed with the 65nm technology. In existing method the factors in terms of power, delay, power delay product are optimized in high speed and average power consumed is very high and power delay product is more, the noise margin is high and other factors like drive capability are more so in order to resolve this issues we are going to proposed model with 45nm technology.

This simulation of AND Gate with and without faulty occurrence. In multiplexer there may be fault This may lead to improper results, so fault free architecture is very useful to suspect the faults. The performance of the system depends upon the gates used in the design of circuit. The performance of proposed design can increase in terms of power PDP and delay by using limited gates.

The simulation of OR Gate with and without fault a logic operation which gives the value one if at least one operand has the value one, and otherwise gives a value of zero this is an without fault in with fault inverse of OR Gate.

### **III. PROPOSED SYSTEM**

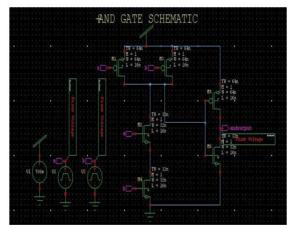

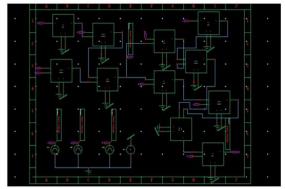

## Fig 1. Schematic of AND gate without fault

The above figure represents the schematic of AND gate which is combinations of number of PMOS and NMOS logic is designed in 65nm technology. It is designed with tanner S-EDIT Tool.

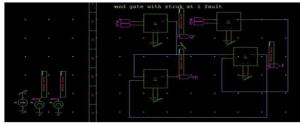

#### Fig 2. Schematic of AND gate with fault

The schematic for a defective AND gate, which combines a number of PMOS and NMOS logic elements, is shown in the above picture. It was created using 65nm technology. It was created using the S-EDIT Tool.

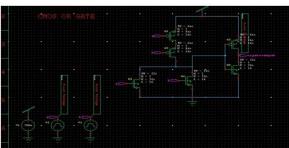

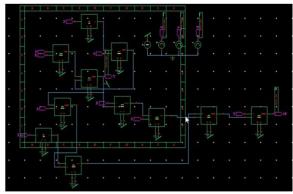

## Fig 3. Schematic of OR gate without fault

The simulation results of an OR gate without a problem are shown in the above image. CMOS Tanner-SPICE (Simulation Program with Integrated Circuit Emphasis) Tool is used to simulate it. W-EDIT is used to analyse wave shapes (wave form editor).

#### Fig 4.Schematic of OR gate with fault

The above figure shows the schematic of faulty OR gate which is combinations of number of PMOS and NMOS logic is designed in 65nm technology. It is designed with tanner S-EDIT fig 5. 2x1 multiplexer without fault.

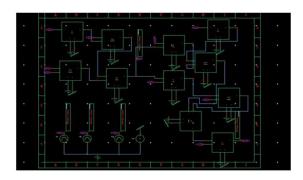

Fig 5. Schematic Of 2X1 MUX without fault

# Fig 6. Schematic Of 2X1 MUX with fault

The above figure shows the schematic of faulty 2X1 MUX which is combinations of number of PMOS and NMOS logic is designed in 65nm

technology .It is designed with tanner S-EDIT Tool.

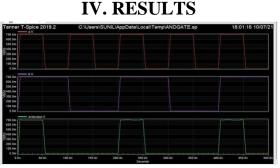

Fig 7. Simulation of AND gate without fault

The graphic above displays the outcomes of a simulation of an AND gate. It is simulated using the CMOS Tanner-SPICE (Simulation Program with Integrated Circuit Emphasis) Tool. Wave shape analysis using W-EDIT (wave form editor).

| anner T-Spice 20 | 19.2 C:\l | C:\Users\SUNIL\AppData\Local\Temp\andgatewithfault.sp |        |                   |        |        |        | 18:44:05 10/07/2 |  |  |

|------------------|-----------|-------------------------------------------------------|--------|-------------------|--------|--------|--------|------------------|--|--|

| 100.0m           |           |                                                       |        |                   |        |        |        |                  |  |  |

| 60.0m            |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m E 1         |           |                                                       |        |                   |        |        |        |                  |  |  |

| b.V              |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m E           |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 3.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0 0m E           |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0m             |           |                                                       |        |                   |        |        |        |                  |  |  |

| VátV             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 000              |           |                                                       |        |                   |        |        |        |                  |  |  |

| 1500             |           |                                                       |        |                   |        |        |        |                  |  |  |

| 000              |           |                                                       |        |                   |        |        |        |                  |  |  |

| 0.0n 50.0n       | 1 100.0n  | 150.0n                                                | 200.01 | 250.0n<br>Seconds | 300.0n | 350.0n | 400.0n | 450.0n           |  |  |

**Fig8.Simulation of AND gate with fault**

The fault AND gate simulation results are shown in the above figure. CMOS Tanner-SPICE (Simulation Program with Integrated Circuit Emphasis) Tool is used to simulate it. W-EDIT is used to analyse wave shapes (wave form editor).

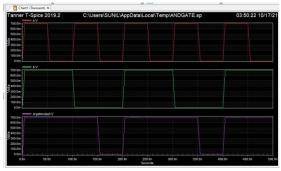

Fig 9. Simulation of OR gate without fault

The simulation results of an OR gate without a problem are shown in the above image. CMOS Tanner-SPICE (Simulation Program with Integrated Circuit Emphasis) Tool is used to simulate it. W-EDIT (wave form editor) is used to examine wave forms).

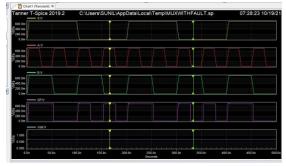

| anner T-Spice 2019.2                       | C:\Users\! | SUNILIA | ppData\Lo | cal\Temp\C | RGATEW | THFAULT.S | P       | 07:00:33 1 | 0/19/2 |

|--------------------------------------------|------------|---------|-----------|------------|--------|-----------|---------|------------|--------|

| 100 0m<br>100 0m<br>1 0m                   |            |         |           |            |        |           |         |            |        |

| 8 V<br>100.0m<br>100.0m<br>100.0m<br>10 0m |            |         |           |            |        |           |         |            |        |

| 00.0m<br>00.0m<br>00.0m<br>0.0m            |            |         |           |            |        |           |         |            |        |

| 100 0m<br>100 0m<br>100 0m<br>0 0m         |            |         |           |            |        |           |         |            |        |

| 0 0 0 50 0 50 0 50 0 50 0 50 0 50 0 50     | 100 Da     | 150 de  | 202.5%    | 250 00     | 300 Pn | 350 0m    | 400 (cm | 450.00     |        |

Fig 10. Simulation of Faulty OR Gate

The fault OR gate simulation results are shown in the above figure. CMOS Tanner-SPICE (Simulation Program with Integrated Circuit Emphasis) Tool is used to simulate it. W-EDIT is used to analyse wave shapes (wave form editor).

Fig 11. Simulation Of Faulty 2X1 Mux

The simulation results of a flawed 2x1 mux are shown in the above graphic. CMOS Tanner's SPICE (Simulation Program with Integrated Circuit Emphasis) Tool is used to model it. W-EDIT (wave form editor) is used to examine wave forms).

## **v. CONCLUSION**

Since the multiplexer plays a crucial role in many systems, malfunctions in the multiplexer cause the systems' findings to be erroneous. To prevent failures, fault tolerant systems must include a fault tolerant multiplexer. The self-repairing multiplexers that are being suggested may be employed in multipliers, multi-bit adders, etc. To achieve 100% error recoverability, the suggested selfrepairing multiplexers may be used in fault tolerant systems. Without the need for outside assistance, the structure can restore itself. This stays away from the space above. The outputs of the circuits are checked by simulation. The suggested structures' fault tolerance is confirmed.

## REFERENCES

[1] Akbar, Muhammad Ali & Lee, JeongA. (2014). "Self-repairing adder using fault localization" MicroelectronicsReliability. 54.

10.1016/j.microrel.2014.02.033. -1451.

[2] Pankaj kumar, Rajendra Kumar Sharma "Real-time fault tolerant full adder design for critical applications" Engineering Science and Technology, Volume 19, Issue 3, September 2016, Pages 1465-1472.

[3] C. Wu, S. Lin, K. Lee and S. M. Reddy, "A Repair-for-Diagnosis Methodology for Logic Circuits," in IEEE

Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 11, pp. 2254-2267, Nov. 2018. doi: 10.1109/TVLSI.2018.2856527.

[4] Koal T, Ulbricht M, Vierhaus HT. Vitual TMR scheme combining fault tolerance and self repair. In: 16th Euromicro IEEE conference on digital system design (DSD 2013); 2013. p. 235– 42.

[5] Smith JE, Lam P. A theory of totally self-checking system design. IEEE Trans Comput 1983;C-32:831–44.

[6] S. gupta, A. Jasuja and R. shandilya, "Real-time fault tolerant full adder using fault localization," 2018 IEEE International Students' Conference on Electrical, Electronics and Computer Science (SCEECS), Bhopal, 2018,pp.1-6. doi: 10.1109/SCEECS.2018.8546908.

[7] Smith JE, Lam P. A theory of totally self-checking system design. IEEE Trans Comput 1983;C-32:831–44.

[8] Jha NK, Wang S-J. Design and synthesis of self checking VLSI circuits. IEEE Trans Comput – Aided Des Integr Circ Syst 1993;12:878–87. 6.

[9] Angskun T, Fagg G, Bosilca G, Pjesivac-Grbovic J, Dongarra J. Selfhealing network for scalable faulttolerant runtime environments. Future Generat Comput Syst 2010;26(3):479–85.

[10] Majumdar A, Nayyar S, Sengar JS. Fault tolerant ALU system 2012. In: International conference on computing sciences (ICCS); 2012. p. 255–60.

[11] Fazeli M, Namazi A, Miremadi SG, Haghdoost A. Operand width aware hardware reuse: a low cost fault-tolerant approach to ALU design in embedded processors. Microelectron Reliab 2011;51(12):2374–87. [12] Koal T, Scheit D, Schölzel M, Vierhaus HT. On the feasibility of builtin self repair for logic circuits. In: IEEE international symposium on defect and fault tolerance VLSI in and nanotechnology systems; 2011. p. 316-24. [13] Khedhiri C, Karmani M, Hamdi B. Concurrent error detection adder based on two paths output computation. In: 2011 Ninth IEEE international symposium on parallel and distributed processing with applications workshops (ISPAW);2011. p. 27-32.

[14] Mitra S, McCluskey EJ. Which concurrent error detection scheme to choose In: Proceedings IEEE international test conference; 2000. p. 985–94.

[15] Sarada Musala and Avireni Srinivasulu, "Self testing and fault secure XOR/XNOR circuit using FinFETs" in proc. of the IEEE International Conference on Communication and Signal Processing - ICCSP' 16, Melmaruvathur, Tamilnadu, India, pp. 976-980, April 6-8, 2016. DOI: 10.1109/ICCSP.2016.77543, Scopus Cited.

[16] Vasudevan DP, Lala PK, Parkerson JP. Self-checking carry-select adder design based on two-rail encoding. IEEE Trans Circ Syst I, Reg Papers 2007;54(12):2696– 705.

[17] B. Sai Krishna, P. Vijaya Lakshmi, Sarada Musala, "Fault Resistant 8- Bit Vedic Multiplier Using Repairable Logic", IEEE International Conference on Emerging Trends in Science and Engineering, Sept. 18- 19, 2019, Scopus Cited.

[18] Sarada Musala and B.R. Shekara Reddy, "Analysis of low power full adder based on dpl and transmission gates", International conference on innovations in

e-ISSN: 2348-6848 p-ISSN: 2348-795X Vol. 9 Issue 07 July 2022

electronics and communication engineering (iciece2014), Guru nanak institute of technology, ibrahimpatnam, July 2014.